- Dipartimento

Presentazione

Governance

Contact us

- Ricerca

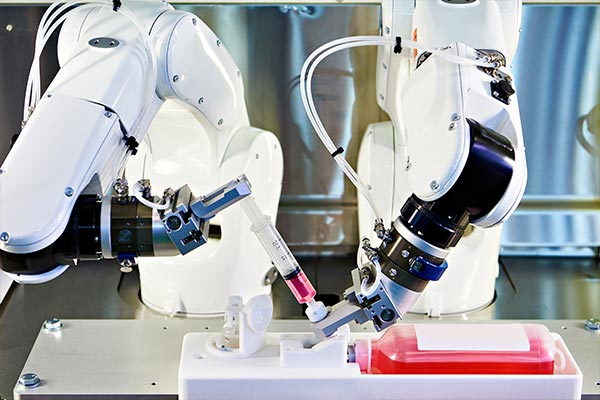

Attività di ricerca

- Didattica

Corsi di Studio

PhD programmes and postgraduate training

- Territorio e società

Servizi per il territorio

Information for community

Contact us

- People

- contacts

-